基于异构多核架构的全高清H.264解码系统网络化工程设计与实现

随着多媒体应用的普及和高清视频需求的爆发式增长,高效、实时的视频解码系统成为数字处理领域的关键。基于异构多核处理器(如ARM + DSP/GPU/FPGA组合)的全高清H.264解码系统,以其优异的性能功耗比和灵活性,成为解决这一挑战的主流方案。本文将探讨此类解码系统的核心设计,并重点阐述其在网络系统工程中的集成与设计考量。

一、 异构多核H.264解码系统核心架构设计

- 处理器选型与任务划分:

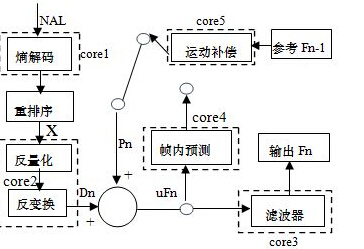

- 控制核心:通常选用高性能、低功耗的ARM Cortex-A系列处理器,负责系统控制、任务调度、网络协议栈处理、用户交互及码流解析(如NAL单元解析、序列参数集/图像参数集解码)。

- 计算核心:针对H.264解码中计算密集型的模块(如熵解码、反量化、反变换、运动补偿、去块滤波),采用专用计算单元。例如,使用DSP进行高效的定点运算,利用GPU的并行处理能力进行宏块级或帧级并行解码,或采用FPGA实现高度定制化的流水线处理。这种异构分工充分发挥了各核的优势。

- 存储子系统设计:

- 采用层次化存储结构,包括片上高速缓存(L1/L2)、共享内存和外部DDR。需精心设计数据布局,减少核间数据搬运开销,尤其是参考帧、当前帧数据在ARM与加速核之间的高效传递。

- 核间通信与同步机制:

- 基于共享内存、邮箱寄存器或高速总线(如AXI)实现。设计高效的消息传递或数据流模型,确保解码任务流水线的顺畅,避免处理单元因等待数据而空闲。

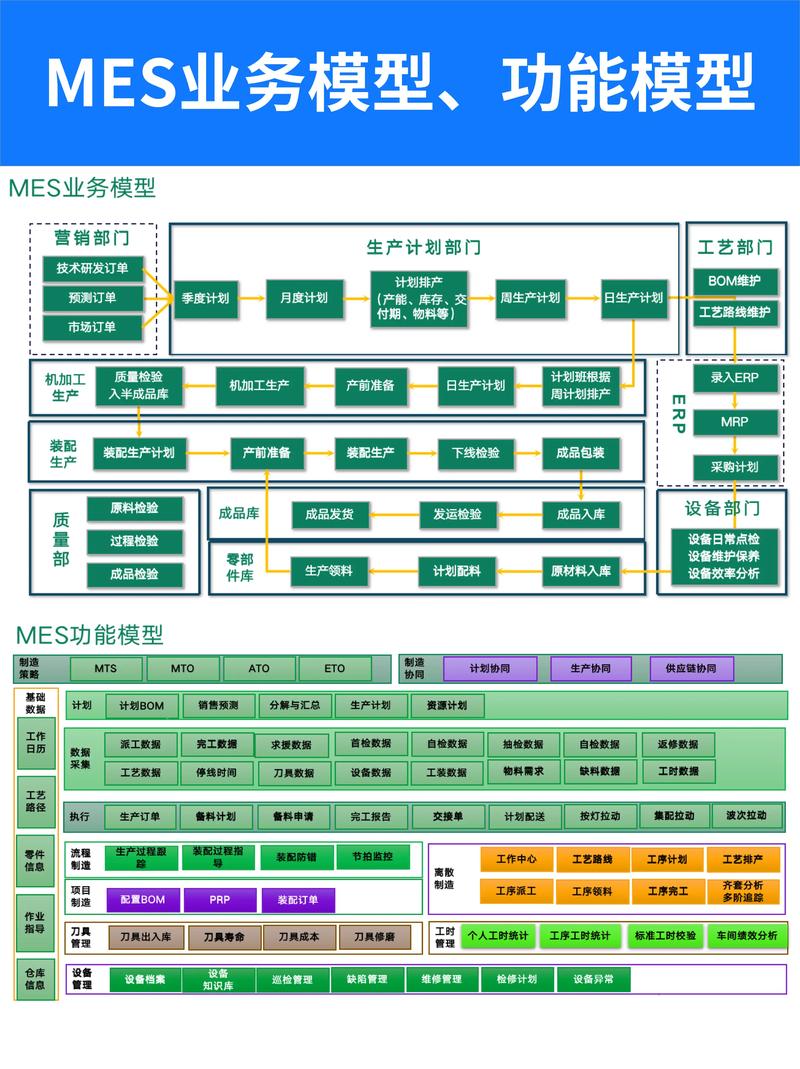

二、 解码算法在异构平台上的并行化与优化

- 功能级并行:将解码流程(如熵解码、重排序、宏块解码)映射到不同的处理单元,形成流水线。

- 数据级并行:在GPU或众核DSP上,对帧内多个宏块或切片(Slice)进行并行解码,这是提升全高清(1080p)解码速率的关键。

- 指令级优化:针对特定计算核心(如DSP的SIMD指令集)对关键算法(如IDCT、运动补偿插值)进行深度优化。

三、 网络系统工程集成设计

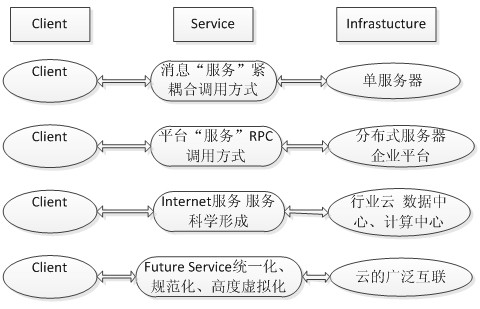

将上述异构解码系统作为网络中的一个智能节点进行设计,需考虑以下层面:

- 网络接口与协议处理:

- 在ARM控制核上集成以太网MAC/PHY或无线网络模块(如Wi-Fi)。

- 实现完整的TCP/IP协议栈,并针对实时视频流优化UDP/RTP协议的处理。支持RTSP用于点播控制,或TS over UDP/IP用于广播流接收。

- 设计网络抖动缓冲区和丢包重传/错误隐藏机制,保障解码的连续性与实时性。

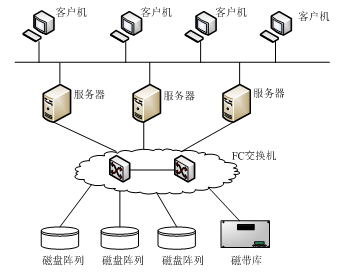

- 流媒体服务与客户端架构:

- 服务器端:系统可作为嵌入式流媒体服务器,从存储设备或前端采集器获取H.264码流,通过网络协议分发给多个客户端。

- 客户端端:系统作为播放终端,接收网络码流,送入异构解码流水线,解码后的帧缓冲通过显示控制器输出。

- 需设计高效的数据通路:

网络接口 → DMA → 内存(码流缓冲区)→ ARM(协议解析、调度)→ 共享内存/直接通路 → 计算核心(解码)→ 帧缓冲区 → 显示输出。

- 系统管理与监控:

- 实现基于Web或专用协议的远程管理接口,允许网络管理员配置解码参数、查看系统状态(如CPU负载、网络带宽、解码帧率)。

- 设计看门狗和故障恢复机制,确保系统在网络异常或局部失效时能保持稳定或快速重启。

- 功耗与热管理:

- 在网络负载和解码任务变化时,动态调整各核的工作频率与电压(DVFS),关闭空闲模块,以降低整体功耗,这对于大规模部署的网络系统工程尤为重要。

四、 挑战与展望

设计此类系统的主要挑战在于:软硬件协同设计的复杂性、核间通信与数据一致性的开销、网络延迟与解码实时性的平衡,以及多版本H.264码流(如High Profile)的兼容性。随着编解码标准向H.265/HEVC、AV1演进,以及AI增强视频处理需求的兴起,异构多核系统的设计需要更高的可编程性和智能化任务调度能力,并与边缘计算、5G网络更深度地融合,以构建更高性能、更低延迟的分布式视频处理网络系统工程。

基于异构多核的全高清H.264解码系统设计,是一个跨越芯片架构、视频算法、操作系统和网络通信的综合性工程。成功的网络系统工程实现,不仅要求解码内核的高效,更依赖于整个数据链路与网络接口的优化设计,从而在复杂的网络环境中提供稳定、高清、实时的视频服务。

如若转载,请注明出处:http://www.ccloud-tech.com/product/35.html

更新时间:2026-04-16 12:42:35